| 緯亞電子 | SMT專業貼片加工為您提供最適合的解決方案 |

公司地址:昆山市周市鎮宋家港路259號

公司電話Tel:0512-50139595

電子郵件Email: steven@pcbvia.com

昆山smt 美史丹佛大學(Stanford University)的研究人員們在日前舉辦的2014年際電子元件會議(IEDM)上展示了真正的 3D 晶片。大部份的 3D 晶片采用矽穿孔(TSV)的方式推疊不同的制造晶片,例如美光科技(Micron Technology)的混合記憶體立方體(HMC)推疊 DRAM 晶粒。

此外,總部設于美奧勒岡州的新創公司BeSang將其專有制程技術授權給南韓的海力士半導體(SK Hynix Inc.),用于打造出無需透過 TSV 的真正 3D 技術。

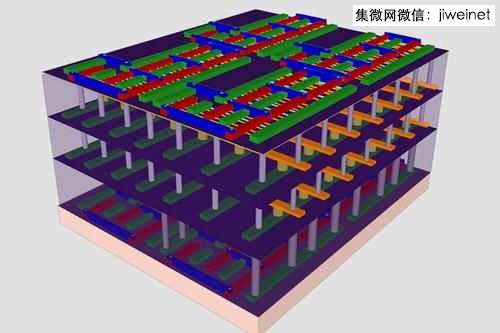

然而,史丹佛大學所展示的是任何晶圓廠都能在標準的互補式金屬氧化物半導體(CMOS)上堆疊任何層數的邏輯與記憶體。在IEDM上,史丹佛大學在 CMOS 晶片上堆疊了2層的金屬氧化物電阻型隨機存取記憶體(PRAM),以及1層利用碳奈米管(CNT)作為電晶體通道的邏輯電路。

史丹佛大學展示的3D晶片以標準過孔方式連接4層電路,底層是標準CMOS,上層是碳奈米管邏輯電晶體,中間夾著2層RRAM。

“對于使用傳統的跨層過孔而言, TSV 技術至關重要,但關鍵在于如果你想達到無法以 TSV 實現的極高能源密度效率之時,”史丹佛大學電子工程系教授Subhasish Mitra表示,“然而,我們能夠利用傳統過孔分別在各層之上順利地打造這些電路層,顯示我們的方法是可行的。”

史丹佛大學所采用的方法是在底層制造一種標準 CMOS 邏輯晶片,然后以二氧化矽絕緣體加以覆蓋,并且利用氬氣濺鍍蝕刻的方式使其平面化。在二層的 RRAM 是由氮化鈦、氧化鉿(作為主動交換層)和鉑組成,然后在 CMOS 層上以200℃的溫度利用傳統 TSV進行制造(以免損壞 CMOS ),以實現互連。

然后,在經過 PRAM 以及另一層絕緣二氧化矽沈積后,另一層絕緣二氧化矽則沈積于 RRAM 之上并實現平面化。上層則先以碳奈米管進行同向覆蓋,利用剝離(lift-off)方式形成石英晶片。為了實現足夠的密度,研究人員們進行13次的碳奈米管轉換方式。然后再用傳統的內層過孔(ILV)與微影技術,將碳奈米管制造于邏輯層上的電晶體通道中。

“我們可以利用這種技術制造出任意層數,”史丹佛大學教授H.S. Philip Wong說:“我們使用相當寬松的設計規則在學校的晶圓廠中制造這些電路層,但在其他的展示中則已證明我們的制程能一直微縮到現有采用過孔技術的20nm商用級。”

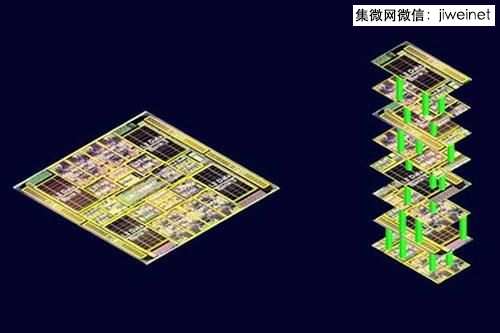

標準的平面型CMOS晶片(圖左)透過TSV分別堆疊邏輯元件與記憶體于不同的結構;史丹佛大學的工程師為采用標準TSV的CMOS晶片上3層結構進行低溫制程,以實現更高密度。

史丹佛大學的研究人員們還積極地展示在平面二氧化矽表面的碳奈米管性能,這是在平行碳奈米管上層利用標準圖形化技術,在場效電晶體(FET)中形成每通道約50個奈米管。研究人員們認為,這種碳奈米管電晶體由于具備較矽晶更高10倍的能效,因而可望在未來取代矽晶電晶體技術。

“我們想表達的是你可以先以標準矽晶 CMOS 作為底層,仍然能夠打造出 3D 晶片,但在未來,我們希望人們轉換成利用碳奈米管電晶體,因為他們的性能可進一步擴展到超越矽晶,這就是為什么我們展示真正的碳奈米管電路,而不只是堆疊上的一個測試電晶體。”

研究團隊們強調,必須確保這種碳奈米層在溫度夠低的情況下制造,才不至于損壞 PRAM ,而在足夠的低溫下制造 PRAM ,才不會損壞到底層的 CMOS 晶片。數以千計的過孔實現各層的互連,才能使得這種碳奈米管場效電晶體(CNTFET)成為 PRAM 的理想選擇。

來源:研究人員以碳納米管實現真正的3D芯片 本文《研究人員以碳納米管實現真正的3D芯片》由昆山緯亞電子有限公司發布在分類[行業新聞],未經許可,嚴禁轉載發布。

本文《研究人員以碳納米管實現真正的3D芯片》由昆山緯亞電子有限公司發布在分類[行業新聞],未經許可,嚴禁轉載發布。

上一篇:三星14nm芯片工藝已投產

下一篇:珠海一家LED線路板廠發生火災